数字逻辑电路——数电实验1

实验1 门电路逻辑功能测试

内容一:与非门和异或门逻辑功能的测试

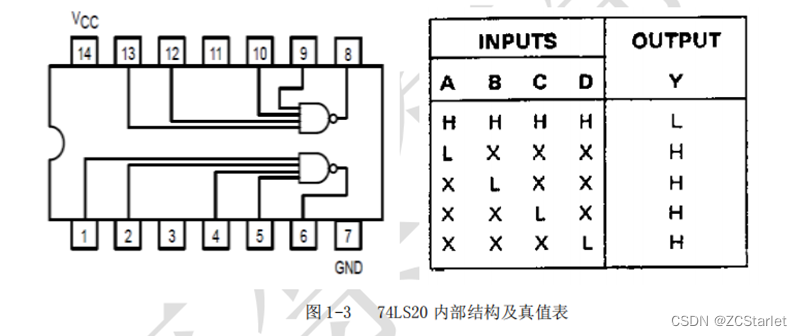

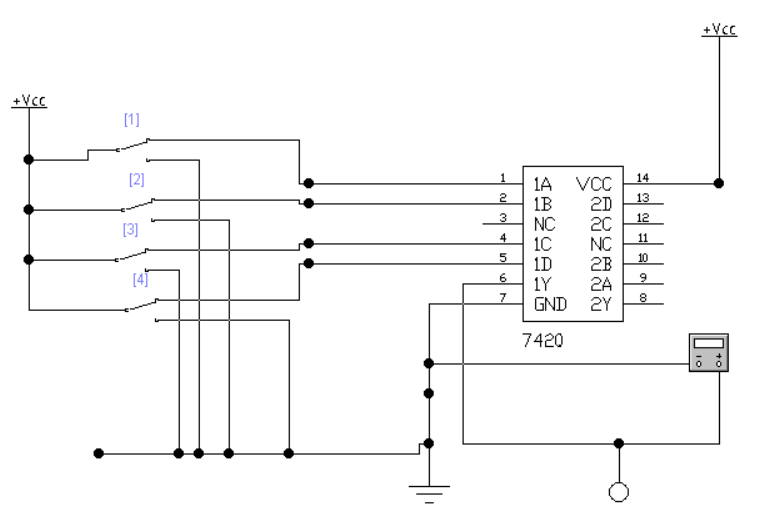

74LS20双4输入与非门逻辑功能测试

74LS20功能:四输入双与非门,其内部结构及真值表如图

电路图如下

| A | B | C | D | Y |

|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 |

全1出0,有0出1

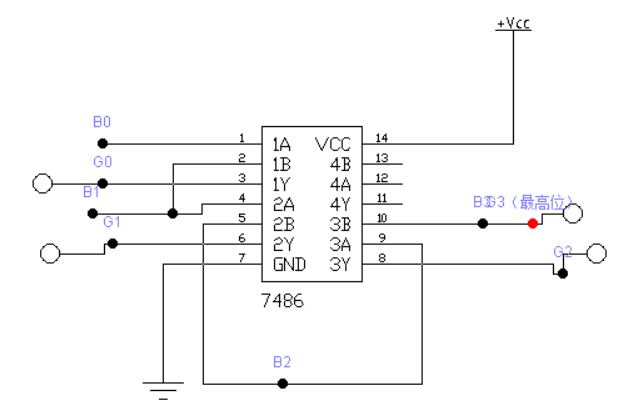

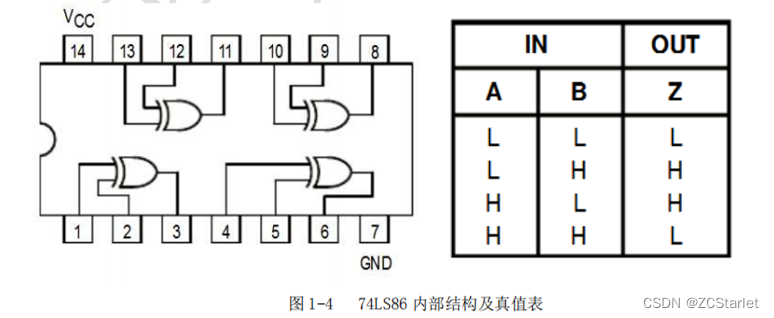

74LS86四2输入异或门逻辑功能测试

74LS86功能:二输入端四异或门,其内部结构及真值表如图

电路图如下

| 1 | 2 | 3 | 4 | A | B | Y |

|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 1 | 1 | 0 |

内容二:根据电路图写出逻辑关系表达式

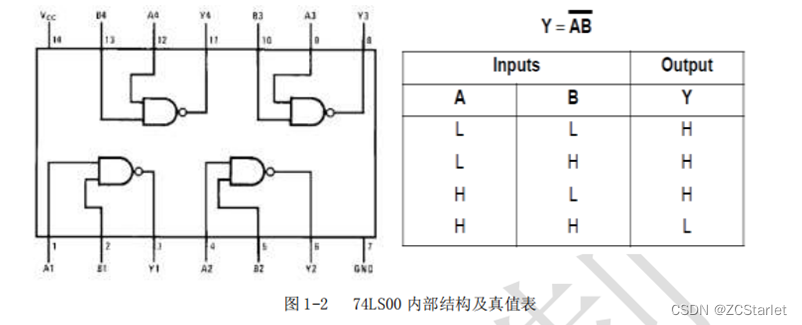

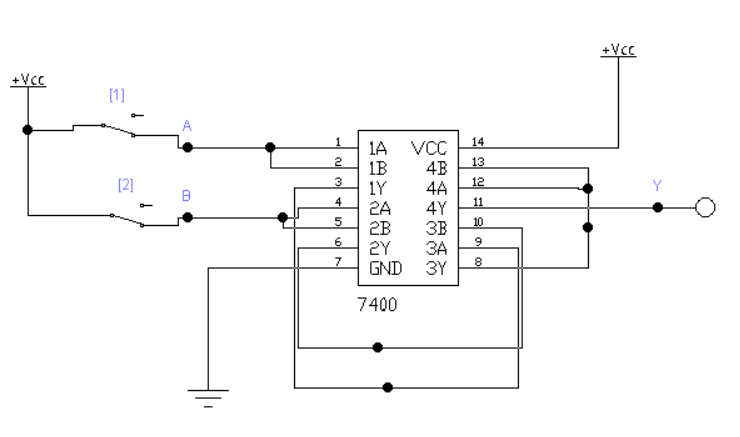

用74LS00按图接线,将输入输出逻辑关系分别填入表中。

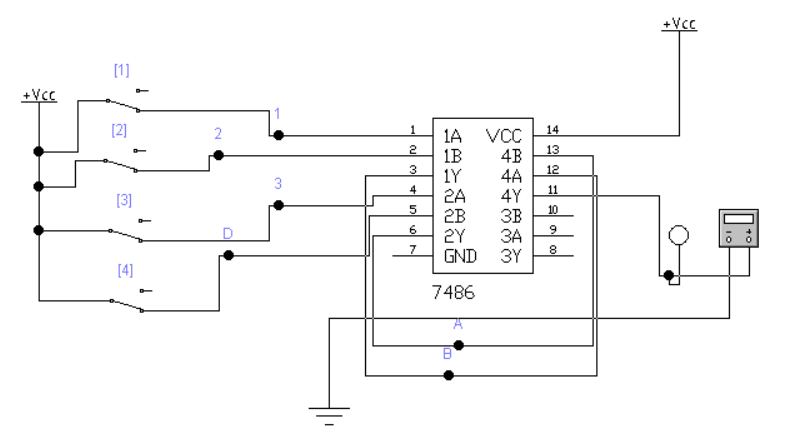

74LS00功能:二输入端四与非门,其内部结构及真值表如图

题目如下

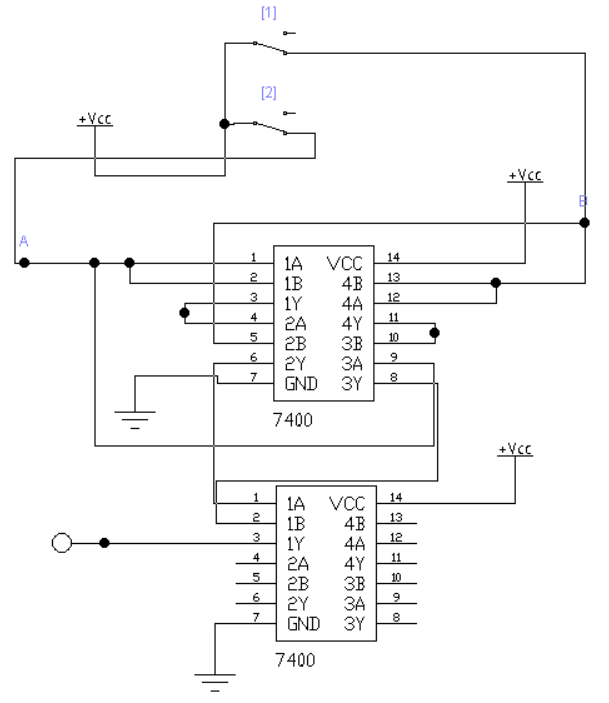

电路图如下

| A | B | Y |

|---|---|---|

| 1 | 1 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 0 | 0 | 0 |

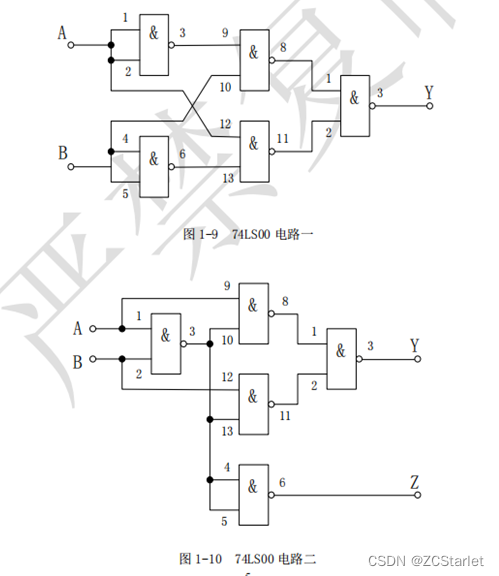

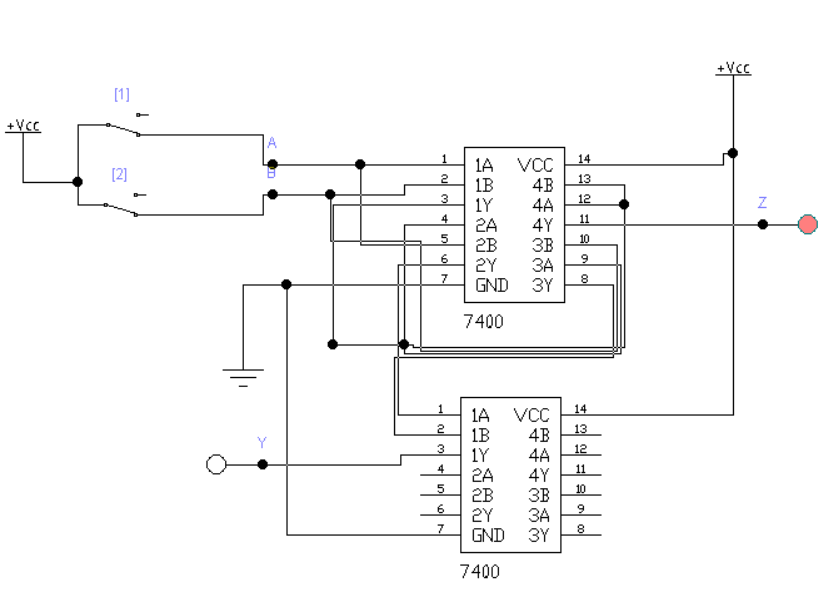

电路图如下

| A | B | Y | Z |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 |

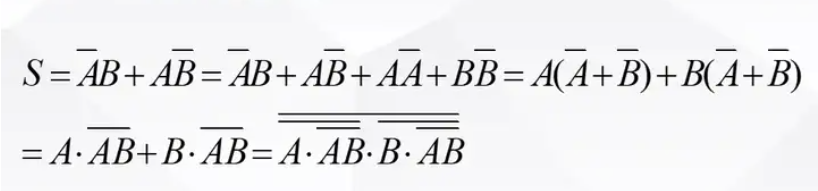

写出两个电路逻辑表达式

电路逻辑表达式为 ĀB + B̄A

电路逻辑表达式为 Y = ĀB + B̄A Z = AB

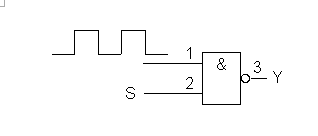

内容三:利用与非门控制输出

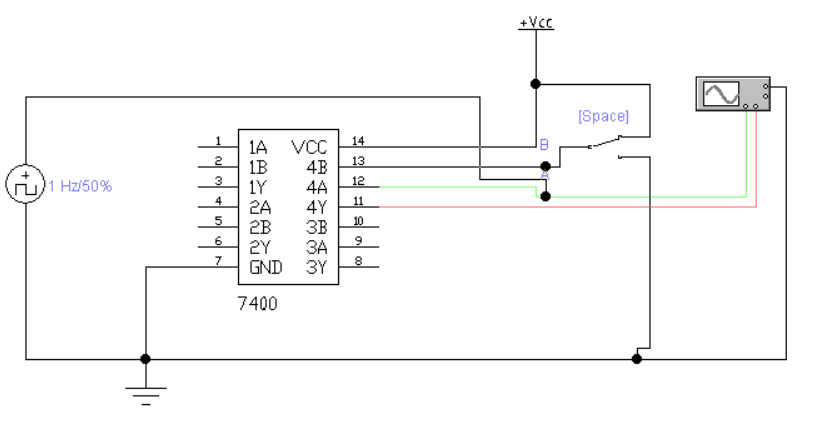

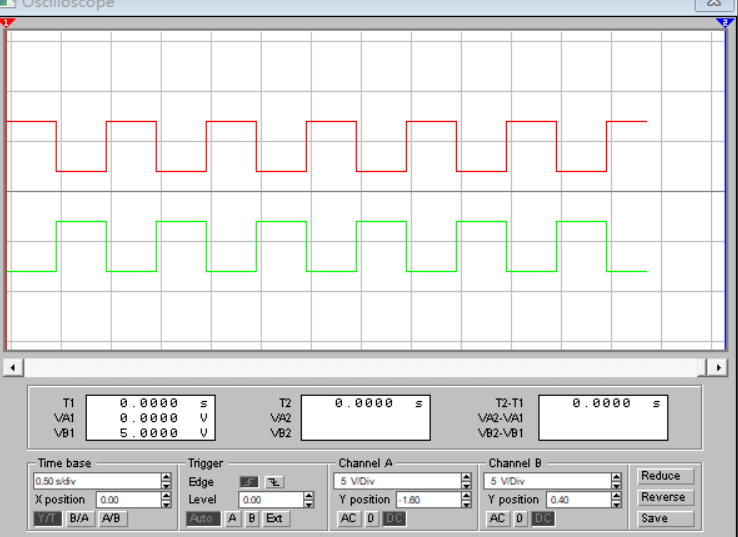

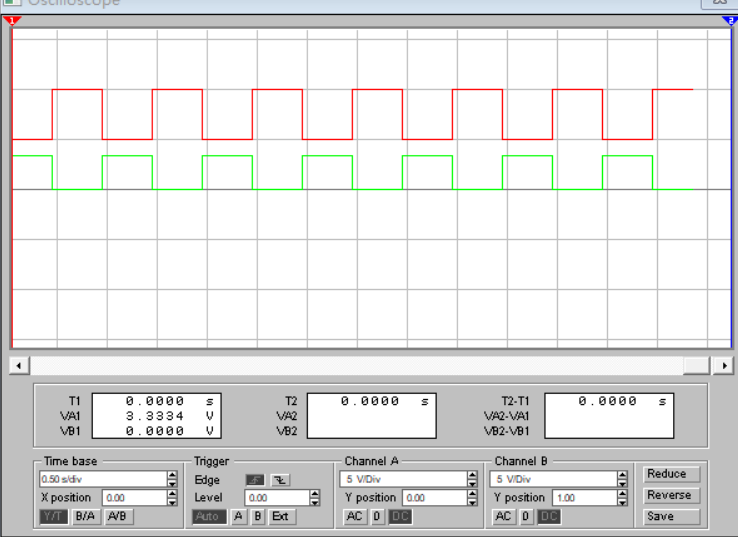

用一片74LS00按图接线,S接任一电平开关,用示波器观察S对输出脉冲的控制作用

第一题

电路图如下

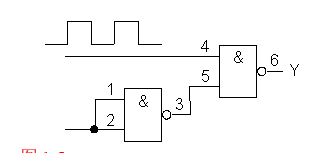

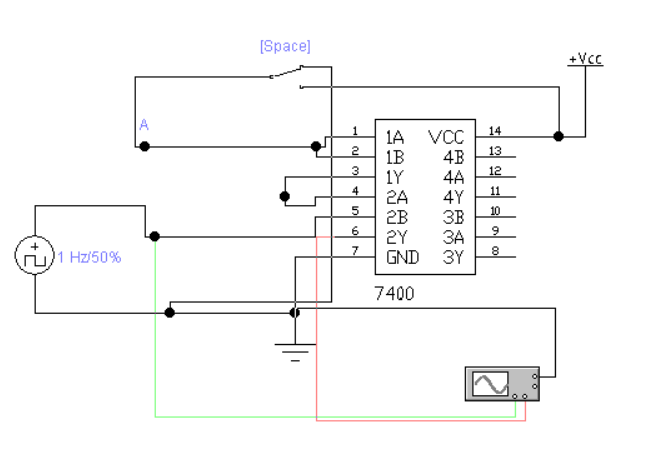

第二题

电路图如下

内容四:用与非门组成其它门电路并测试验证

第一题:组成或非门

用一片2输入端四与非门组成或非门

电路图如下

| A | B | Y |

|---|---|---|

| 1 | 1 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 0 | 0 | 1 |

第二题:组成异或门

同内容二

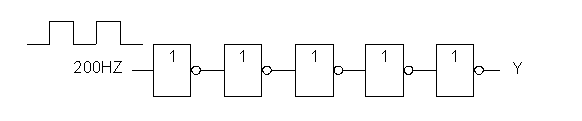

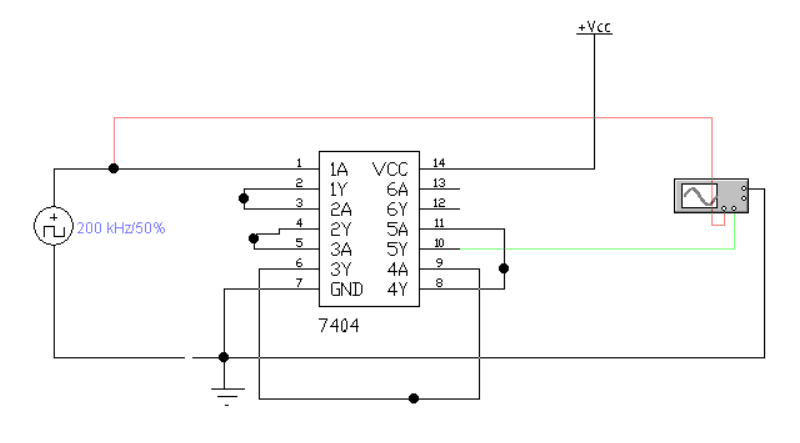

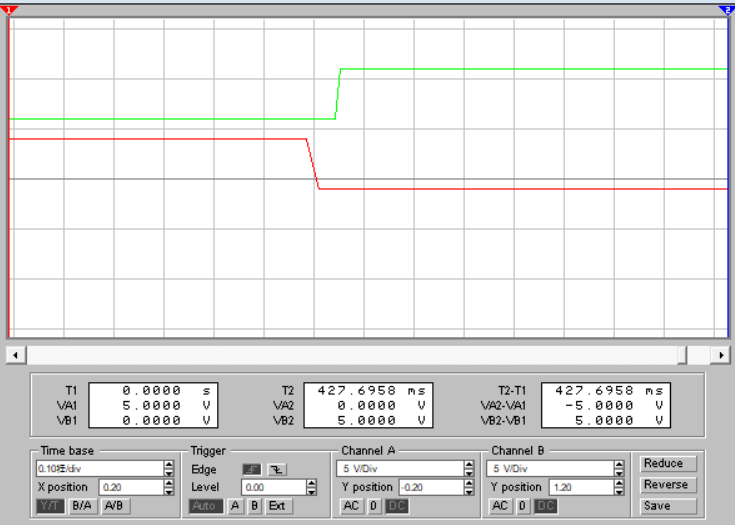

内容五:逻辑门传输延迟时间的测量

用六反相器(非门)按图接线,输入200KHz连续脉冲,用双踪示波器测量输入、输出相位差,计算每个门的平均传输延迟时间的值。

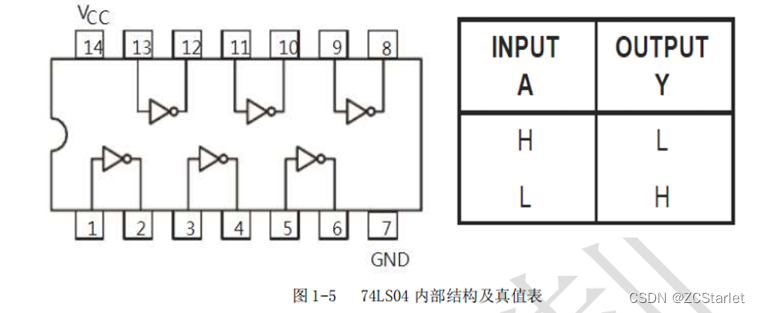

74LS04功能:六反相器,其内部结构及真值表如图

电路图如下

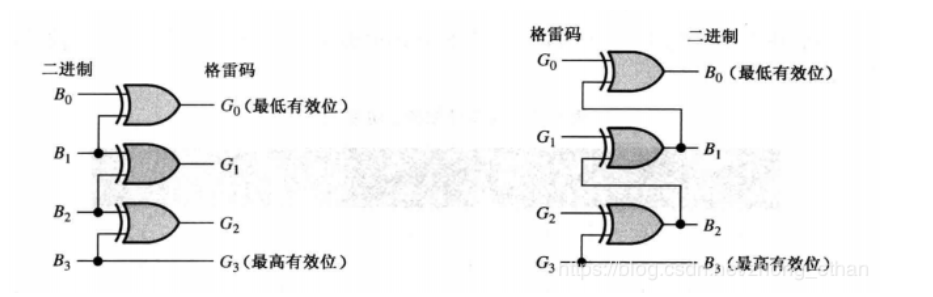

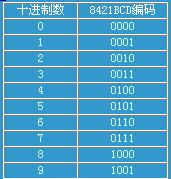

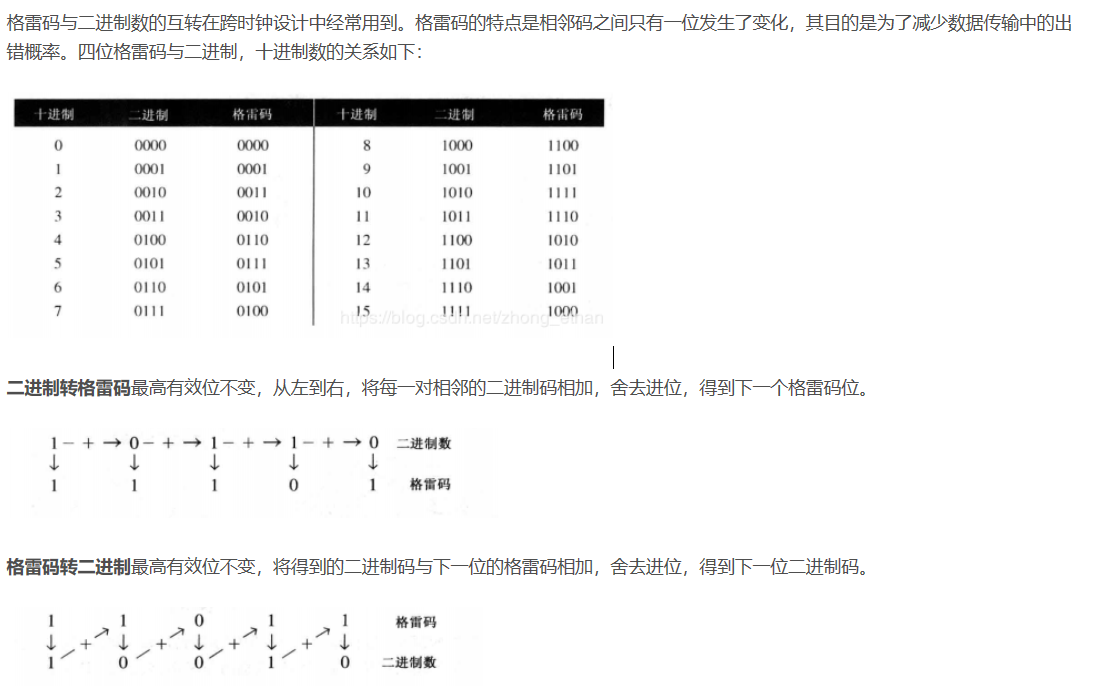

内容六:用基本门电路组装一个译码电路:将BCD8421码转换成格雷码

BCD8421码:二进制编码的十进制数,简称BCD码

一位不产生进位的加法电路用异或门就可以实现,下图左边为一个二进制-格雷码转换器器,右边为一个格雷码-二进制码转换器。